altium designer 15

v10.0- 介紹說明

- 下載地址

- 精品推薦

- 相關軟件

- 網友評論

altium designer 2015官方版不僅會大大提高你的工作效率,而且當你有了設計靈感也再也不用擔心會流失,簡單的操作,隨時隨地都能記錄下來,運行速度也是非常的快,感興趣的朋友不如來極光下載站看看吧!

altium designer相關版本推薦 | ||

| ad20 | ad18 | ad17 |

| ad16 | ad15 | ad14 |

| ad13 | ad10 | ad09 |

| ad綠色版 | ||

軟件亮點

多邊形鋪銅檢查

我們增加了多邊形鋪銅的擴展檢查。在鋪銅過程中,將按照鋪銅順序自動檢查相關性,避免生成重疊的多邊形鋪銅。

板框間隙檢查

我們擴展了間隙檢查選項,支持PCB對象和定義的板框邊緣之間的間隙檢查。這能提供更精確的間隙檢查,更好地控制元件放置。

增強的Union功能

PCB面板新增了一個Union版塊,協助您管理設計數據。Union面板會顯示設計項目中所有的Union類型、Union以及Union數據基元,并與設計中的其它PCB對象完美兼容。

xDxDesigner Importer

將原理圖設計從xDxDesigner導入至Altium Designer的新工具,可以節省大量重建原理圖設計的時間。

Cypress CapSense

我們在集成庫中增加了CapSense接觸式傳感器,您可以在原理圖設計的庫面板中輕松訪問。

測試點間隙檢查

通過增強的測試點間隙檢查選項,您可以更好地控制間隙檢查,更容易檢查測試點與通孔焊盤之間、以及測試點之間的距離。

軟件特點

xSignals管理功能提升:現在,利用xSignals向導即可自動進行高速設計的長度匹配,它可以自動分析T型分支、元器件、信號對和信號組數據,大大降低了高速設計配置時的時間消耗。

擴展的軟硬結合支持:軟硬結合設計中的表層可以加上“比基尼(Bikini)”覆蓋層。該覆蓋層在3D效果下可視,并可根據設計師的特殊需求另行配置。設計規則中添加了覆蓋層的邊緣間距和擴展規則,提供了更精確的覆蓋層應用控制。

輸出文檔功能強化:PCB設計可以作為3D PDF輸出,通過pdf閱讀器查看、旋轉3D設計,方便地選擇電路板上的單個元器件,實現更高的精準度,將設計初衷傳遞給制造商。

altium designer 15安裝教程

1.先在本站下載解壓安裝包,然后打開

2.文件解壓完成后,右鍵點擊Altium designer 15 setup文件,彈出對話框,左鍵點擊打開。

3.彈出安裝界面,點擊NEXT。出現安裝協議選擇界面,選擇I accept the agreement,點擊NEXT。

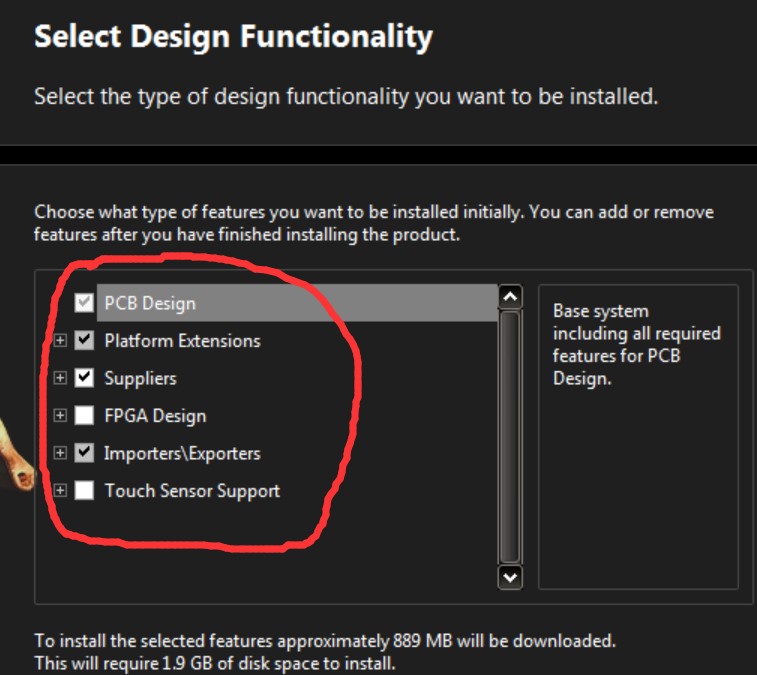

4.出現安裝組件選擇界面,選擇好需要安裝的工具,點擊NEXT。

5.出現安裝目錄選擇界面,選擇安裝目錄為D盤Altium designer 15文件夾,點擊NEXT,然后等待安裝完成即可。

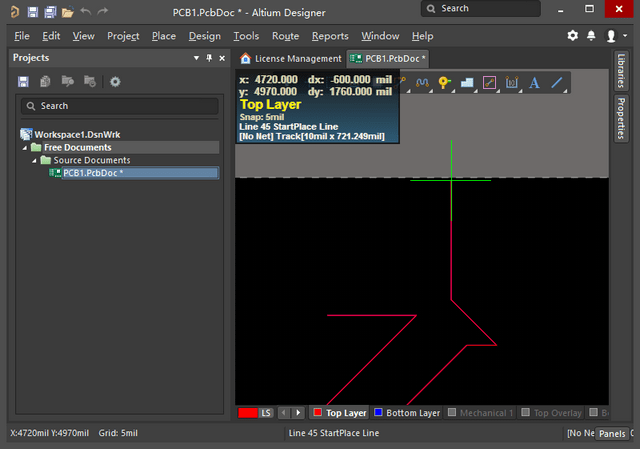

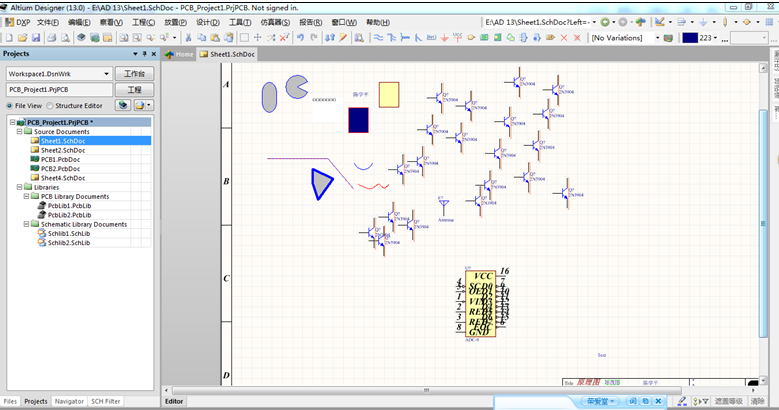

ad15原理圖如何生成pcb

打開Altium Designer軟件,依次點擊菜單“File”->“project”->“PCB Project”新建一個PCB工程文件。

右擊新建的工程,在彈出的列表中選擇“Add New Project”->“Schematic”新建一個原理圖。

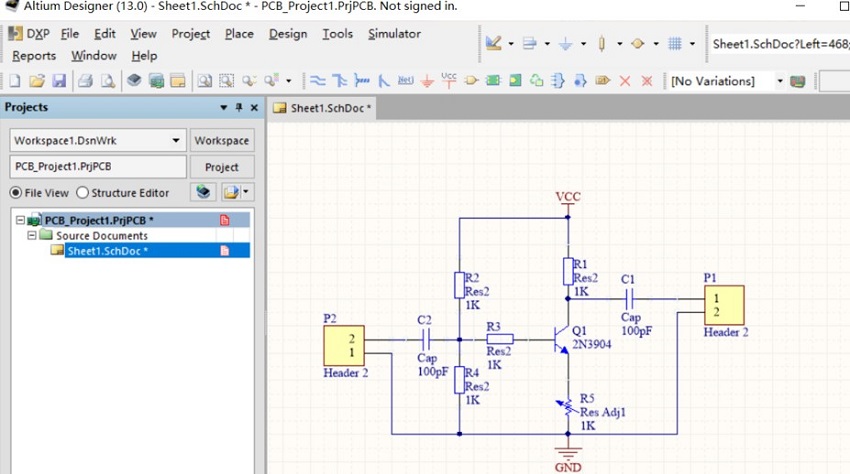

按需求設計好原理圖,分配好各元件的封裝,確認后保存原理圖到當前工程,確保位于當前工程下。

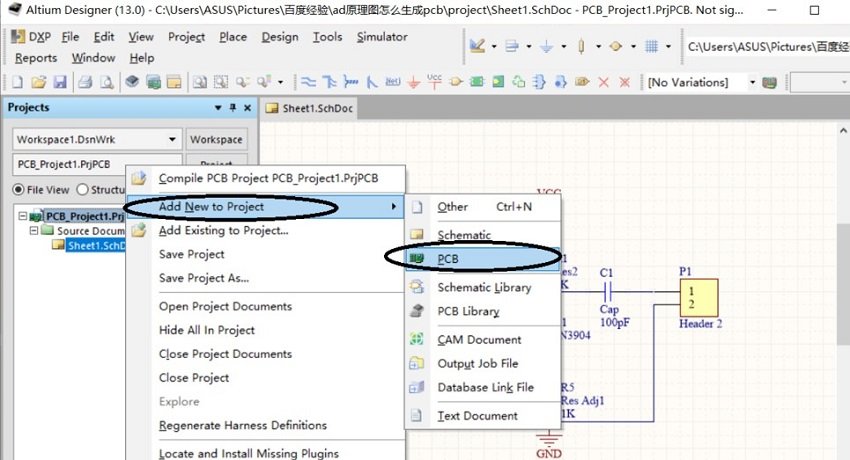

再次右擊當前工程,在菜單列表中選擇“Add New Project”->“PCB”新建一個PCB文件。

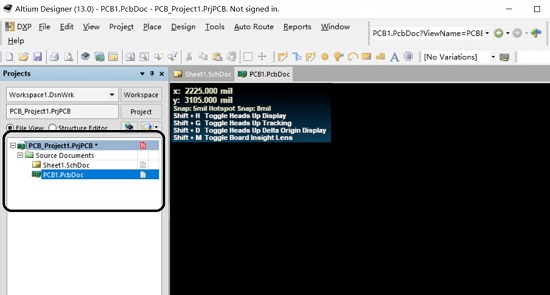

確保PCB位于當前工程,保存PCB文件。

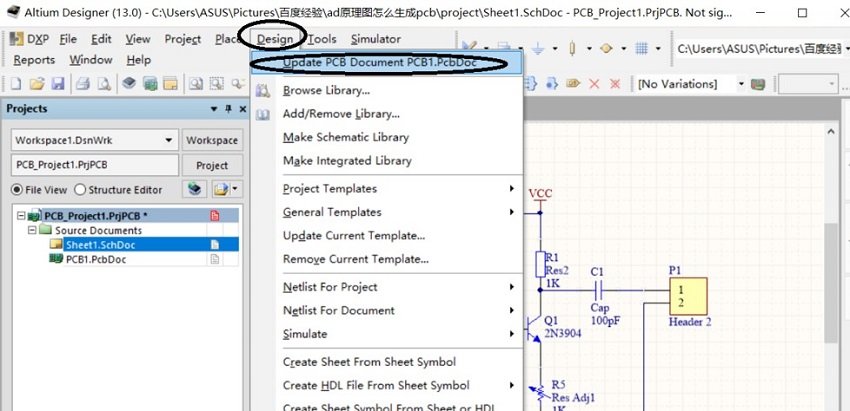

切換到原理圖,點擊“Design”菜單項,在彈出的列表中選擇“Update PCB Document PCB.PcbDoc”,準備生成網絡表,其中“PCB.PcbDoc”是對應的PCB文件名。

若元件封裝無誤,則生成的“Engineering Change Order”不會有錯誤,點擊左下角的“Excute Changes”執行變更,正常情況右側列表應全部為勾勾,接著點擊右下角的“Close”。

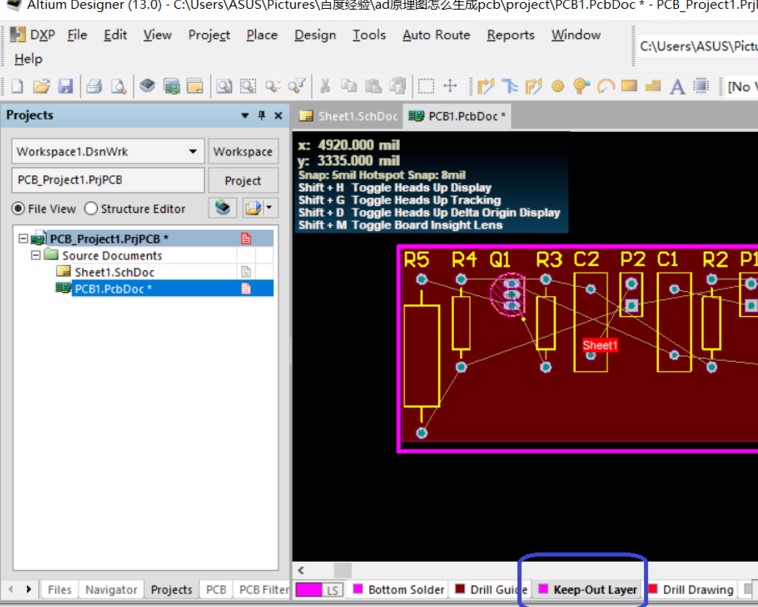

切換到PCB文件,在KeepOutLayer層繪制好板框,將元件布局好。

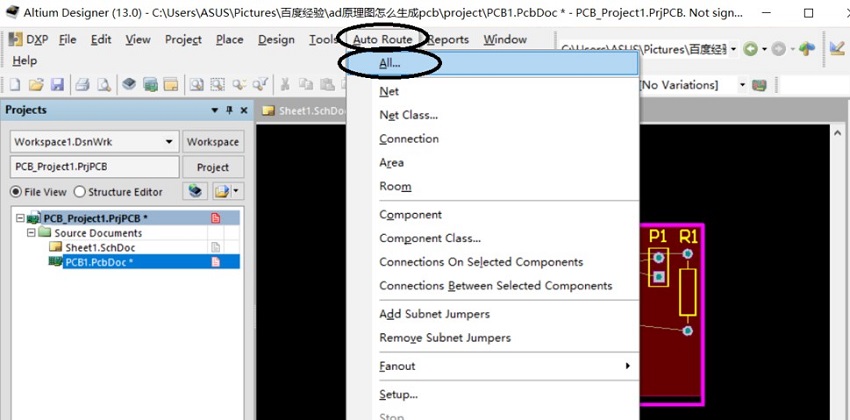

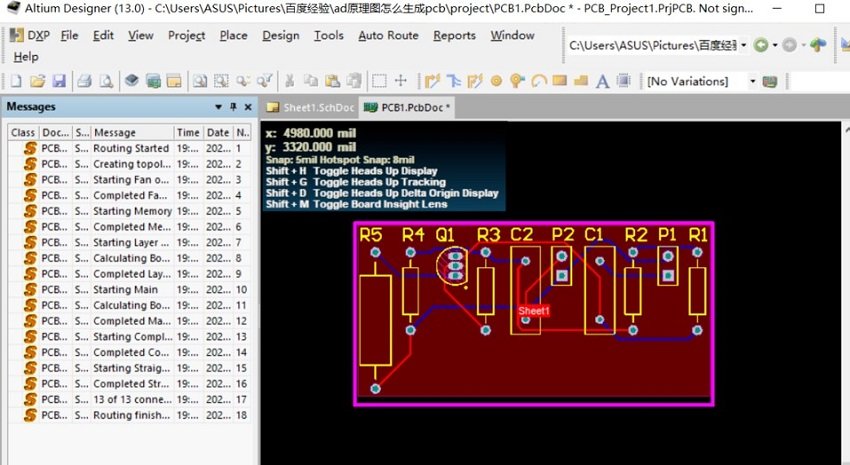

點擊“Auto Route”->“All..”準備自動布線。

保存PCB,至此通過原理圖生成PCB成功!

注意:用于生成網絡表的原理圖和目標PCB應位于同一工程。PCB保存后才能試用原理圖生成到PCB,否則軟件會提示找不到PCB文件。

下載地址

- Pc版

altium designer 15 v10.0

本類排名

本類推薦

裝機必備

換一批- 聊天

- qq電腦版

- 微信電腦版

- yy語音

- skype

- 視頻

- 騰訊視頻

- 愛奇藝

- 優酷視頻

- 芒果tv

- 剪輯

- 愛剪輯

- 剪映

- 會聲會影

- adobe premiere

- 音樂

- qq音樂

- 網易云音樂

- 酷狗音樂

- 酷我音樂

- 瀏覽器

- 360瀏覽器

- 谷歌瀏覽器

- 火狐瀏覽器

- ie瀏覽器

- 辦公

- 釘釘

- 企業微信

- wps

- office

- 輸入法

- 搜狗輸入法

- qq輸入法

- 五筆輸入法

- 訊飛輸入法

- 壓縮

- 360壓縮

- winrar

- winzip

- 7z解壓軟件

- 翻譯

- 谷歌翻譯

- 百度翻譯

- 金山翻譯

- 英譯漢軟件

- 殺毒

- 360殺毒

- 360安全衛士

- 火絨軟件

- 騰訊電腦管家

- p圖

- 美圖秀秀

- photoshop

- 光影魔術手

- lightroom

- 編程

- python

- c語言軟件

- java開發工具

- vc6.0

- 網盤

- 百度網盤

- 阿里云盤

- 115網盤

- 天翼云盤

- 下載

- 迅雷

- qq旋風

- 電驢

- utorrent

- 證券

- 華泰證券

- 廣發證券

- 方正證券

- 西南證券

- 郵箱

- qq郵箱

- outlook

- 阿里郵箱

- icloud

- 驅動

- 驅動精靈

- 驅動人生

- 網卡驅動

- 打印機驅動

網友評論